2025年6月22日的主页超大综合电路技术和电路研讨会(Sympos)

6月22日的Home报道说,英特尔在2025年关于VLSI技术和电路的研讨会上揭示了下一代Intel 18A节点流程的技术细节。该节点将替换现有的Intel 3个节点,以优化电压法规的频率和功能,并将用于处理器级消费者“ Panther Lake”和Clearwater Forest(Pure E-Core Xeon)等产品。根据英特尔工程师的说法,与Intel 3相比,使用功能区(全型栅极GAA)和PowerVia(Backside Dower Supply)技术的Intel 18A工艺已实现了30%以上的密度改善和“全节点性能的改善”,并且还提供了完整的设计功能(HP)和高密度(HD)和高密度(HD)和使用。多亏了RibbonFet技术,与Intel 3使用TheFinfet相比,Intel 18A取得了显着跳跃。功能区的主要优点是:静电栅极性能拟合,单位面积有效宽度较大,PA较低拉西氏能力,并进一步增强了设计的灵活性;通过DTCO(BitCell -Optimization处理过程)和BitCell自定义介绍了180h / 160h库的不同功能宽度,平衡了逻辑能力 /泄漏消耗和性能 - 对SRAM的功能频宽度 - 对SRAM的功能频宽度 - 综合性能增强和潜在的18A Node Chips的潜在设计。此外,18A采用的PowerVia技术,用后侧强度取代前侧痕迹,实现了电源网络的衰减和独立优化,从而实现了许多增长:逻辑密度改善了YUNIT的标准使用,可改善RC信号降低电压降低(DROOP)缩小(DROOP)缩小(DROOP)缩小(DROOP)缩小缩水

HP / DR库的高度180 / 160NM接触多硅闸门间距50mm金属零层(M0)间距32nm HCC / HDC SRAAM面积0.023 / 0.023 /0.021μm2前金属层数字10ml(低成本,高密度,高密度),14-16ml(高性能)(高性能)(高性能)

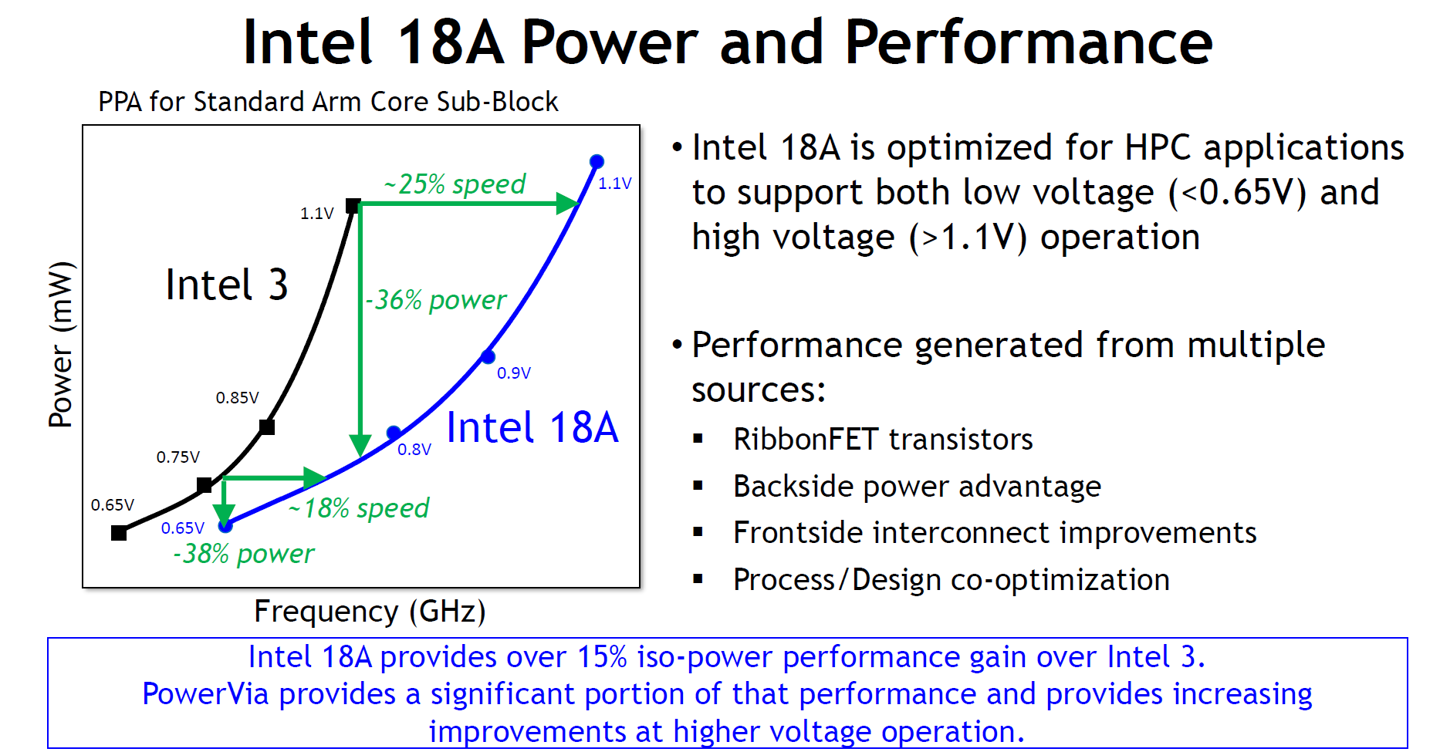

背面3毫升 + 3 ml a的金属层数量与英特尔3相比,Intel 18A的每单位消耗量超过15%:绩效和能源的卓越性:在1.1V时,18A的性能比Intel 3高25%;并支持低于0.65V的低电压操作,每单位的电力消耗量最大为38%。密度改善:与英特尔3相比,18A达到了39%(平均30%)的密度改善,而后侧供应供应可提供8-10%的大学使用,将单元的使用量增加8-10%,并将强烈的IR电压崩溃缩小到原始的10%。参数的比较:HP库的高度从Intel 3的240nm降低到180nm,HD库从210nm降低到160nm; M0/M2金属层间距是 - 从30/42nm到32/32nm的优化。 SRAM缩放:18A高电流电池(HCC)的密度比英特尔3高30%,HCC和HDC SRAM区域分别达到0.0230μm2和0.0210μm2。英特尔说18a流程将继续重复:18A-P和18A-PT衍生版本将于2026-2028启动(IT主页注:在2025 Direct Connect会议上宣布),客户将根据这些节点开放CHIP制造。

6月22日的Home报道说,英特尔在2025年关于VLSI技术和电路的研讨会上揭示了下一代Intel 18A节点流程的技术细节。该节点将替换现有的Intel 3个节点,以优化电压法规的频率和功能,并将用于处理器级消费者“ Panther Lake”和Clearwater Forest(Pure E-Core Xeon)等产品。根据英特尔工程师的说法,与Intel 3相比,使用功能区(全型栅极GAA)和PowerVia(Backside Dower Supply)技术的Intel 18A工艺已实现了30%以上的密度改善和“全节点性能的改善”,并且还提供了完整的设计功能(HP)和高密度(HD)和高密度(HD)和使用。多亏了RibbonFet技术,与Intel 3使用TheFinfet相比,Intel 18A取得了显着跳跃。功能区的主要优点是:静电栅极性能拟合,单位面积有效宽度较大,PA较低拉西氏能力,并进一步增强了设计的灵活性;通过DTCO(BitCell -Optimization处理过程)和BitCell自定义介绍了180h / 160h库的不同功能宽度,平衡了逻辑能力 /泄漏消耗和性能 - 对SRAM的功能频宽度 - 对SRAM的功能频宽度 - 综合性能增强和潜在的18A Node Chips的潜在设计。此外,18A采用的PowerVia技术,用后侧强度取代前侧痕迹,实现了电源网络的衰减和独立优化,从而实现了许多增长:逻辑密度改善了YUNIT的标准使用,可改善RC信号降低电压降低(DROOP)缩小(DROOP)缩小(DROOP)缩小(DROOP)缩小缩水

HP / DR库的高度180 / 160NM接触多硅闸门间距50mm金属零层(M0)间距32nm HCC / HDC SRAAM面积0.023 / 0.023 /0.021μm2前金属层数字10ml(低成本,高密度,高密度),14-16ml(高性能)(高性能)(高性能)

背面3毫升 + 3 ml a的金属层数量与英特尔3相比,Intel 18A的每单位消耗量超过15%:绩效和能源的卓越性:在1.1V时,18A的性能比Intel 3高25%;并支持低于0.65V的低电压操作,每单位的电力消耗量最大为38%。密度改善:与英特尔3相比,18A达到了39%(平均30%)的密度改善,而后侧供应供应可提供8-10%的大学使用,将单元的使用量增加8-10%,并将强烈的IR电压崩溃缩小到原始的10%。参数的比较:HP库的高度从Intel 3的240nm降低到180nm,HD库从210nm降低到160nm; M0/M2金属层间距是 - 从30/42nm到32/32nm的优化。 SRAM缩放:18A高电流电池(HCC)的密度比英特尔3高30%,HCC和HDC SRAM区域分别达到0.0230μm2和0.0210μm2。英特尔说18a流程将继续重复:18A-P和18A-PT衍生版本将于2026-2028启动(IT主页注:在2025 Direct Connect会议上宣布),客户将根据这些节点开放CHIP制造。